## Simulink<sup>®</sup> HDL Coder™ 2 User's Guide

# MATLAB® SIMULINK®

#### **How to Contact MathWorks**

(a)

www.mathworks.comWebcomp.soft-sys.matlabNewsgroupwww.mathworks.com/contact\_TS.htmlTechnical Support

suggest@mathworks.com bugs@mathworks.com doc@mathworks.com service@mathworks.com info@mathworks.com Product enhancement suggestions Bug reports Documentation error reports Order status, license renewals, passcodes Sales, pricing, and general information

508-647-7000 (Phone) 508-647-7001 (Fax)

The MathWorks, Inc. 3 Apple Hill Drive Natick. MA 01760-2098

For contact information about worldwide offices, see the MathWorks Web site.

Simulink<sup>®</sup> HDL Coder™ User's Guide

© COPYRIGHT 2006–2011 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

#### **Revision History**

| September 2006 | Online only | New for Version 1.0 (Release 2006b)     |

|----------------|-------------|-----------------------------------------|

| March 2007     | Online only | Updated for Version 1.1 (Release 2007a) |

| September 2007 | Online only | Revised for Version 1.2 (Release 2007b) |

| March 2008     | Online only | Revised for Version 1.3 (Release 2008a) |

| October 2008   | Online only | Revised for Version 1.4 (Release 2008b) |

| March 2009     | Online only | Revised for Version 1.5 (Release 2009a) |

| September 2009 | Online only | Revised for Version 1.6 (Release 2009b) |

| March 2010     | Online only | Revised for Version 1.7 (Release 2010a) |

| September 2010 | Online only | Revised for Version 2.0 (Release 2010b) |

| April 2011     | Online only | Revised for Version 2.1 (Release 2011a) |

## Contents

### **Getting Started**

| Product Overview          Automated HDL Code Generation in the Hardware         Development Process         Summary of Key Features | 1-2<br>1-2<br>1-4 |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Expected Users and Prerequisites                                                                                                    | 1-5               |

| Software Requirements and Installation<br>Software Requirements<br>Installing the Software                                          | 1-6<br>1-6<br>1-7 |

| Available Help and Demos         Online Help         Demos                                                                          | 1-8<br>1-8<br>1-8 |

### **Introduction to HDL Code Generation**

## 2

| Before You Generate Code                                                                                                                                     | 2-2                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Overview of Exercises                                                                                                                                        | 2-3                      |

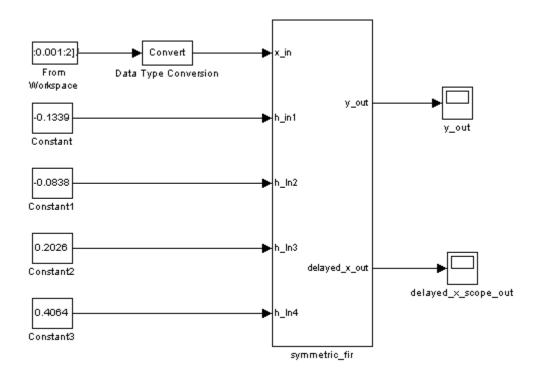

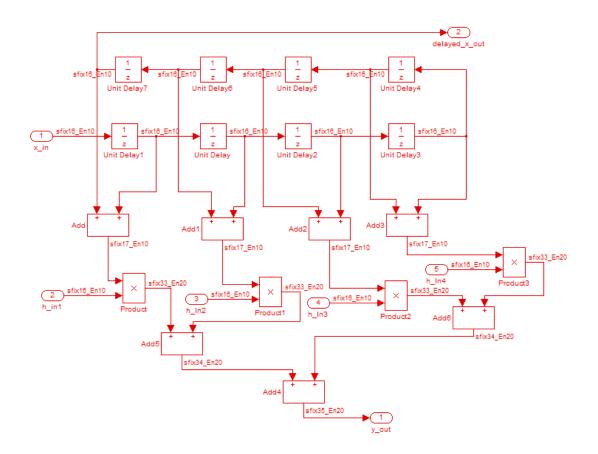

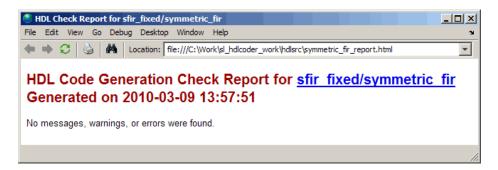

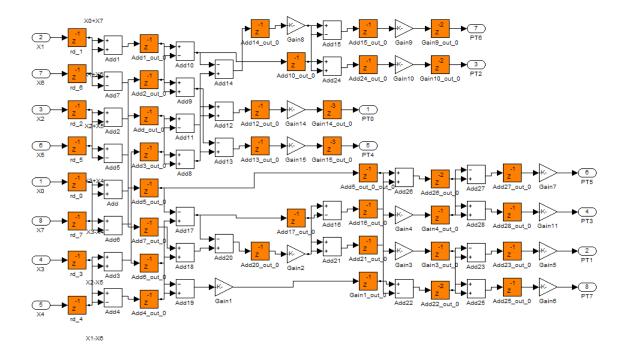

| The sfir_fixed Demo Model                                                                                                                                    | 2-4                      |

| Generating HDL Code Using the Command Line<br>Interface<br>Overview<br>Creating a Folder and Local Model File<br>Initializing Model Parameters with hdlsetup | 2-7<br>2-7<br>2-7<br>2-8 |

| Generating a VHDL Entity from a Subsystem             | 2-10   |

|-------------------------------------------------------|--------|

| Generating VHDL Test Bench Code                       | 2-12   |

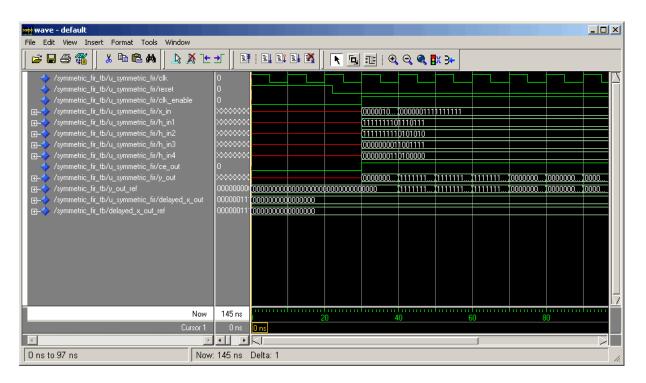

| Verifying Generated Code                              | 2 - 13 |

| Generating a Verilog Module and Test Bench            | 2-14   |

| Generating HDL Code Using the GUI                     | 2-16   |

| Simulink <sup>®</sup> HDL Coder GUI Overview          | 2-16   |

| Creating a Folder and Local Model File                | 2-19   |

| Viewing Coder Options in the Configuration Parameters |        |

| Dialog Box                                            | 2-20   |

| Initializing Model Parameters with hdlsetup           | 2-22   |

| Selecting and Checking a Subsystem for HDL            |        |

| Compatibility                                         | 2-23   |

| Generating VHDL Code                                  | 2-24   |

| Generating VHDL Test Bench Code                       | 2-27   |

| Verifying Generated Code                              | 2-29   |

| Generating Verilog Model and Test Bench Code          | 2-29   |

|                                                       |        |

| Simulating and Verifying Generated HDL Code           | 2-30   |

### Code Generation Options in the Simulink® HDL Coder Dialog Boxes

| Viewing and Setting HDL Code Generation Options   | 3-2  |

|---------------------------------------------------|------|

| HDL Code Generation Options in the Configuration  |      |

| Parameters Dialog Box                             | 3-2  |

| HDL Code Generation Options in the Model Explorer | 3-4  |

| HDL Code Generation Tools Menu                    | 3-6  |

| HDL Code Generation Options in the Block Context  |      |

| Menu                                              | 3-6  |

| The HDL Block Properties Dialog Box               | 3-8  |

| HDL Code Generation Pane: General                 | 3-9  |

| HDL Code Generation Top-Level Pane Overview       | 3-11 |

| Generate HDL for                                  | 3-13 |

| Language                                          | 3-14 |

| Folder                                            | 3-15 |

| Code Generation Output                            | 3-16 |

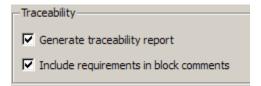

| Generate traceability report                            | 3-17         |

|---------------------------------------------------------|--------------|

| Include requirements in block comments                  | 3-18         |

| Generate optimization report                            | 3-19         |

| Generate resource utilization report                    | 3-20         |

|                                                         |              |

| HDL Code Generation Pane: Global Settings               | 3-21         |

| Global Settings Overview                                | 3-21<br>3-24 |

| Reset type                                              | 3-24         |

| Reset asserted level                                    | 3-26         |

| Clock input port                                        | 3-20<br>3-27 |

| Clock enable input port                                 | 3-28         |

| Reset input port                                        | 3-29         |

| Clock inputs                                            | 3-30         |

| Oversampling factor                                     | 3-31         |

| Comment in header                                       | 3-32         |

| Verilog file extension                                  | 3-32<br>3-33 |

| VHDL file extension                                     | 3-33<br>3-34 |

| Entity conflict postfix                                 | 3-35         |

| Package postfix                                         | 3-36         |

| Reserved word postfix                                   | 3-37         |

| Split entity and architecture                           | 3-38         |

| Split entity file postfix                               | 3-40         |

| Split arch file postfix                                 | 3-40<br>3-41 |

| Clocked process postfix                                 | 3-41<br>3-42 |

| Enable prefix                                           | 3-42<br>3-43 |

| Pipeline postfix                                        | 3-45<br>3-44 |

| Complex real part postfix                               | 3-44<br>3-45 |

| Complex real part postix                                | 3-45<br>3-46 |

| Input data type                                         | 3-40<br>3-47 |

| Output data type                                        | 3-48         |

| Clock enable output port                                | 3-40<br>3-50 |

| Balance Delays                                          | 3-50<br>3-51 |

| Scalarize Vector Ports                                  | 3-51<br>3-52 |

| Represent constant values by aggregates                 | 3-52<br>3-53 |

| Use "rising_edge" for registers                         | 3-53<br>3-54 |

| Loop unrolling                                          | 3-55         |

|                                                         | 3-56         |

| Cast before sum<br>Use Verilog `timescale directives    | 3-50<br>3-57 |

| Inline VHDL configuration                               | 3-57<br>3-58 |

| Concatenate type safe zeros                             | 3-50<br>3-59 |

| Emit time/date stamp in header                          | 3-59<br>3-60 |

| Optimize timing controller                              | 3-60<br>3-62 |

| Minimize clock enables                                  | 3-64         |

| Minimize clock enables<br>Minimize intermediate signals | 3-64<br>3-66 |

| winninge intermediate signals                           | 9-00         |

| HDL Code Generation Pane: Test Bench            | 3-67  |

|-------------------------------------------------|-------|

| Test Bench Overview                             | 3-69  |

| HDL test bench                                  | 3-70  |

| Cosimulation blocks                             | 3-71  |

| Cosimulation model for use with:                | 3-73  |

| Test bench name postfix                         | 3-74  |

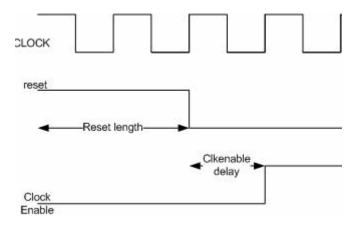

| Force clock                                     | 3-75  |

| Clock high time (ns)                            | 3-76  |

| Clock low time (ns)                             | 3-77  |

| Hold time (ns)                                  | 3-78  |

| Setup time (ns)                                 | 3-79  |

| Force clock enable                              | 3-80  |

| Clock enable delay (in clock cycles)            | 3-81  |

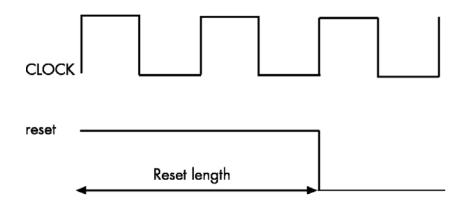

| Force reset                                     | 3-83  |

| Reset length (in clock cycles)                  | 3-84  |

| Hold input data between samples                 | 3-86  |

| Initialize test bench inputs                    | 3-87  |

| Multi-file test bench                           | 3-88  |

| Test bench reference postfix                    | 3-90  |

| Test bench data file name postfix               | 3-91  |

| Ignore output data checking (number of samples) | 3-92  |

|                                                 |       |

| HDL Code Generation Pane: EDA Tool Scripts      | 3-94  |

| EDA Tool Scripts Overview                       | 3-96  |

| Generate EDA scripts                            | 3-97  |

| Generate multicycle path information            | 3-98  |

| Compile file postfix                            | 3-99  |

|                                                 | 3-100 |

| Compile command for VHDL                        | 3-101 |

| Compile command for Verilog                     | 3-102 |

| Compile termination                             | 3-103 |

| Simulation file postfix                         | 3-104 |

| Simulation initialization                       | 3-105 |

|                                                 | 3-106 |

| 8                                               | 3-107 |

| Simulation termination                          | 3-108 |

|                                                 | 3-109 |

|                                                 | 3-111 |

|                                                 |       |

|                                                 | 3-112 |

|                                                 |       |

### Specifying Block Implementations and Parameters for HDL Code Generation

### 4

| Overview of Block Implementations and                |             |

|------------------------------------------------------|-------------|

| Implementation Parameters                            | 4-2         |

| A Note on Control Files                              | 4-3         |

|                                                      | <b>H</b> -0 |

| Viewing Plack Implementation and Implementation      |             |

| Viewing Block Implementation and Implementation      |             |

| Parameter Settings in the HDL Block Properties       |             |

| Dialog Box                                           | 4-5         |

|                                                      |             |

| Selecting Block Implementations and Setting          |             |

| Implementation Parameters with the HDL Block         |             |

| Properties Dialog Box                                | 4-9         |

|                                                      |             |

| Selecting Block Implementations with hdlset_param    | 4-16        |

| Screening block implementations with huiset_param    | 110         |

|                                                      |             |

| Selecting Implementations and Setting Implementation |             |

| Parameters for Multiple Blocks                       | 4-20        |

|                                                      |             |

| Obtaining HDL-Related Block and Model Parameter      |             |

| Information                                          | 4-22        |

| Obtaining Block-level HDL Settings                   | 4-22        |

| Obtaining Model-level HDL Settings                   | 4-24        |

| -                                                    |             |

### Guide to Supported Blocks and Block Implementations

| Generating a Supported Blocks Quick Reference<br>Report | 5-2  |

|---------------------------------------------------------|------|

| Summary of Block Implementations                        | 5-3  |

| Blocks with Multiple Implementations                    | 5-32 |

| Overview       Implementations for Commonly Used Blocks         Math Function Block Implementations       Divide Block Implementations         Divide Block Implementations       Implementations         Subsystem Interfaces and Special-Purpose       Implementations | 5-32<br>5-33<br>5-39<br>5-44<br>5-45 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| A Note on Cascade Implementations                                                                                                                                                                                                                                        | 5-46                                 |

| Block-Specific Usage, Requirements, and Restrictions                                                                                                                                                                                                                     |                                      |

| for HDL Code Generation                                                                                                                                                                                                                                                  | 5-47                                 |

| Block Usage, Requirements, and Restrictions                                                                                                                                                                                                                              | 5-47                                 |

| Restrictions on Use of Blocks in the Test Bench                                                                                                                                                                                                                          | 5-58                                 |

| Block Implementation Parameters                                                                                                                                                                                                                                          | 5-60                                 |

| Overview                                                                                                                                                                                                                                                                 | 5-60                                 |

| ConstMultiplierOptimization                                                                                                                                                                                                                                              | 5-61                                 |

| CoeffMultipliers                                                                                                                                                                                                                                                         | 5-62                                 |

| Distributed Arithmetic Implementation Parameters for                                                                                                                                                                                                                     | 0 01                                 |

| Digital Filter Blocks                                                                                                                                                                                                                                                    | 5-65                                 |

| DistributedPipelining                                                                                                                                                                                                                                                    | 5-75                                 |

| InputPipeline                                                                                                                                                                                                                                                            | 5-84                                 |

| OutputPipeline                                                                                                                                                                                                                                                           | 5-85                                 |

| Pipelining Implementation Parameters for Filter Blocks                                                                                                                                                                                                                   | 5-86                                 |

| RÂM                                                                                                                                                                                                                                                                      | 5-90                                 |

| ResetType                                                                                                                                                                                                                                                                | 5-90                                 |

| ShiftRegister                                                                                                                                                                                                                                                            | 5-92                                 |

| UseRAM                                                                                                                                                                                                                                                                   | 5-93                                 |

| Speed vs. Area Optimizations for FIR Filter                                                                                                                                                                                                                              |                                      |

| Implementations                                                                                                                                                                                                                                                          | 5-95                                 |

| Interface Generation Parameters                                                                                                                                                                                                                                          | 5-101                                |

|                                                                                                                                                                                                                                                                          |                                      |

| Blocks That Support Complex Data                                                                                                                                                                                                                                         | 5-103                                |

| Complex Coefficients and Data Support for the Digital                                                                                                                                                                                                                    | 0 100                                |

| Filter and Biquad Filter Blocks                                                                                                                                                                                                                                          | 5-107                                |

|                                                                                                                                                                                                                                                                          | 5-107                                |

| Support for Lookup Table Blocks in HDL Code                                                                                                                                                                                                                              |                                      |

| Generation                                                                                                                                                                                                                                                               | 5-108                                |

| n-D Lookup Table                                                                                                                                                                                                                                                         | 5-108                                |

| Prelookup                                                                                                                                                                                                                                                                | 5-109                                |

| Direct Lookup Table (n-D)                                                                                                                                                                                                                                                | 5-110                                |

| 1-D Lookup Table                                                                                                                                                                                                                                                         | 5-111                                |

| 2-D Lookup Table                                                                                                                                                                                                                                                         | 5-111                                |

| ±                                                                                                                                                                                                                                                                        | =                                    |

| C | Overview of Multirate Models                                                                        |

|---|-----------------------------------------------------------------------------------------------------|

| 0 | Configuring Multirate Models for HDL Code                                                           |

|   | Generation                                                                                          |

|   | Overview                                                                                            |

|   | Configuring Model Parameters                                                                        |

|   | Configuring Sample Rates in the Model<br>Constraints for Rate Transition Blocks and Other Blocks in |

|   | Multirate Models                                                                                    |

| F | Example: Model with a Multirate DUT                                                                 |

| 6 | enerating a Global Oversampling Clock                                                               |

|   | Why Use a Global Oversampling Clock?                                                                |

|   | Requirements for the Oversampling Factor                                                            |

|   | Specifying the Oversampling Factor From the GUI                                                     |

|   | Specifying the Oversampling Factor From the Command<br>Line                                         |

|   | Resolving Oversampling Rate Conflicts                                                               |

| 6 | Generating Multicycle Path Information Files                                                        |

|   | Overview                                                                                            |

|   | Format and Content of a Multicycle Path Information<br>File                                         |

|   | File Naming and Location Conventions                                                                |

|   | Generating Multicycle Path Information Files Using the<br>GUI                                       |

|   | Generating Multicycle Path Information Files Using the<br>Command Line                              |

|   | Limitations                                                                                         |

|   | Example of Generating a Multicycle Path Information<br>File                                         |

|   | Гис                                                                                                 |

| F | Properties Supporting Multirate Code Generation                                                     |

|   | Overview                                                                                            |

|   | HoldInputDataBetweenSamples                                                                         |

|   | OptimizeTimingController                                                                            |

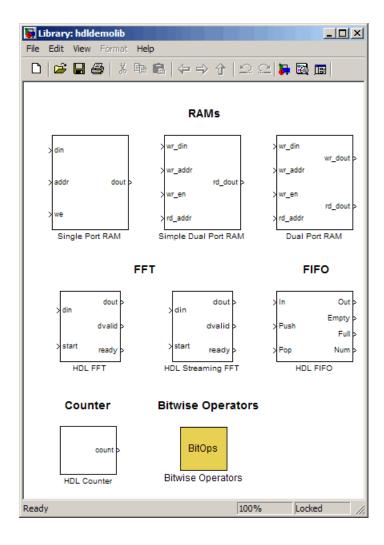

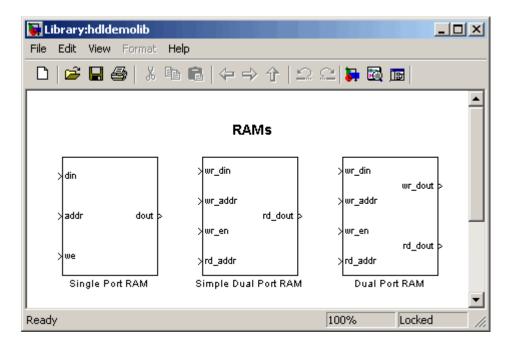

| RAM Bloc              | ks                                         |

|-----------------------|--------------------------------------------|

| Overview              | v of RAM Blocks                            |

|                       | rt RAM Block                               |

|                       | Dual Port RAM Block                        |

| Single Po             | ort RAM Block                              |

|                       | neration with RAM Blocks                   |

|                       | ons for RAM Blocks                         |

| Generic               | RAM and ROM Demos                          |

| HDL Cour              | nter                                       |

| Overview              |                                            |

| Counter               |                                            |

|                       | Ports                                      |

|                       | the Counter Data Type and Size             |

| HDL Im                | plementation and Implementation Parameters |

| Paramet               | ers and Dialog Box                         |

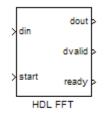

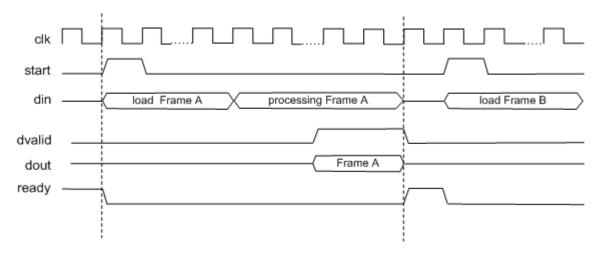

| HDL FFT               |                                            |

|                       | v                                          |

|                       | puts and Outputs                           |

|                       | plementation and Implementation Parameters |

|                       | ers and Dialog Box                         |

| HDL FIFO              | )                                          |

|                       | v                                          |

|                       | puts and Outputs                           |

|                       | plementation and Implementation Parameters |

| -                     | ers and Dialog Box                         |

|                       |                                            |

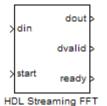

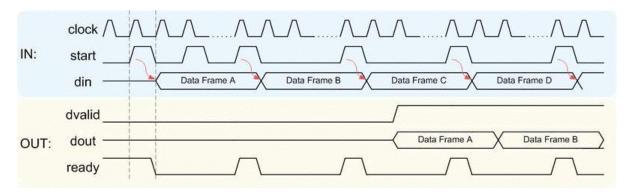

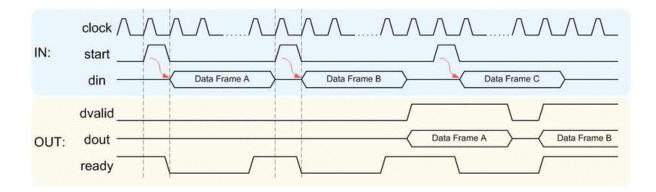

| HDL Strea<br>Overviev | aming FFT                                  |

|                       | eaming FFT Block Demo                      |

|                       | puts and Outputs                           |

|                       | Description                                |

|                       | plementation and Implementation Parameters |

|                       | ers and Dialog Box                         |

| r ar annet            | VIN UITU DIUTUS DUA                        |

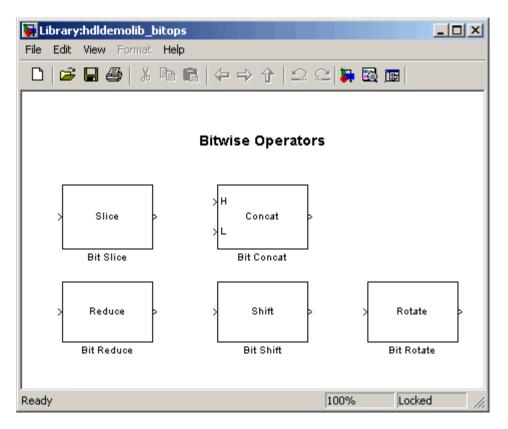

| Bitwise Operators                   | 7-49 |

|-------------------------------------|------|

| Overview of Bitwise Operator Blocks | 7-49 |

| Bit Concat                          | 7-51 |

| Bit Reduce                          | 7-53 |

| Bit Rotate                          | 7-55 |

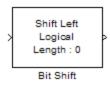

| Bit Shift                           | 7-57 |

| Bit Slice                           | 7-59 |

### Streaming, Resource Sharing, and Delay Balancing

### 8

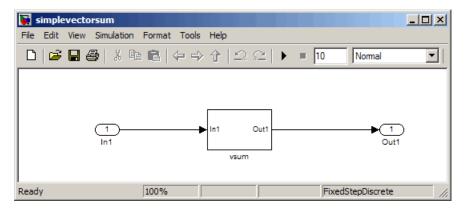

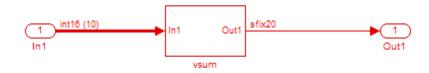

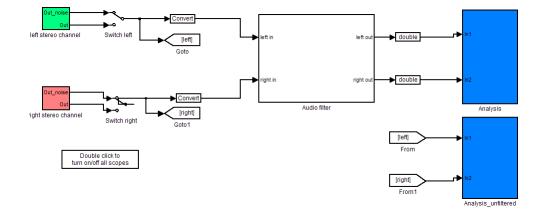

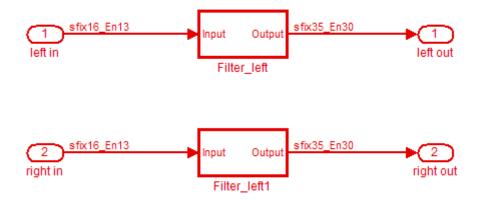

| Streaming                                     | 8-2  |

|-----------------------------------------------|------|

| Streaming Overview                            | 8-2  |

| Streaming Example                             | 8-4  |

| Requirements and Limitations for Streaming    | 8-13 |

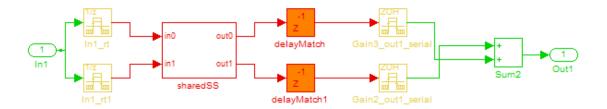

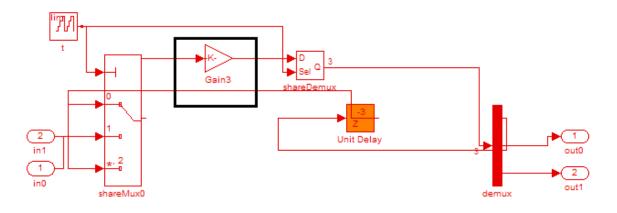

| Resource Sharing                              | 8-16 |

| Overview                                      | 8-16 |

| Mutually Parallel vs. Data-Dependent Resource |      |

| Sharing                                       | 8-19 |

| Resource Sharing with Atomic Subsystems       | 8-30 |

| Resource Sharing Information in Reports       | 8-35 |

| Limitations for Resource Sharing              | 8-35 |

| Delay Balancing                               | 8-37 |

| Properties Supporting Delay Balancing         | 8-37 |

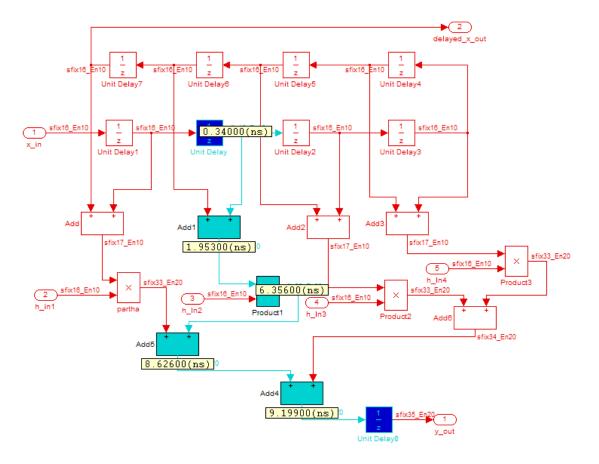

| Delay Balancing Example                       | 8-38 |

| Unsupported Blocks and Block Implementations  | 8-41 |

### Generating Bit-True Cycle-Accurate Models

### 9

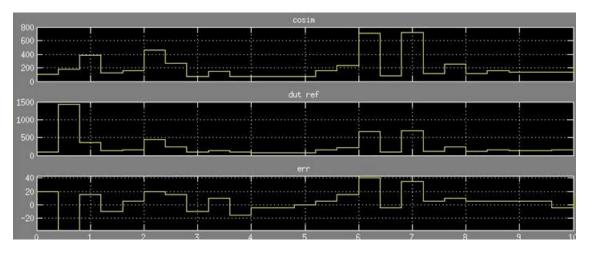

| Example: Numeric Differences                        | 9-4  |

|-----------------------------------------------------|------|

| Example: Latency                                    | 9-7  |

| Defaults and Options for Generated Models           | 9-10 |

| Defaults for Model Generation                       | 9-10 |

| GUI Options                                         | 9-11 |

| Generated Model Properties for makehol              | 9-13 |

| Limitations for Generated Models                    | 9-15 |

| Fixed-Point Limitation                              | 9-15 |

| Double-Precision Limitation                         | 9-15 |

| Model Properties Not Supported for Generated Models | 9-16 |

### Code Generation Reports, HDL Compatibility Checker, Block Support Library, and Code Annotation

## 10

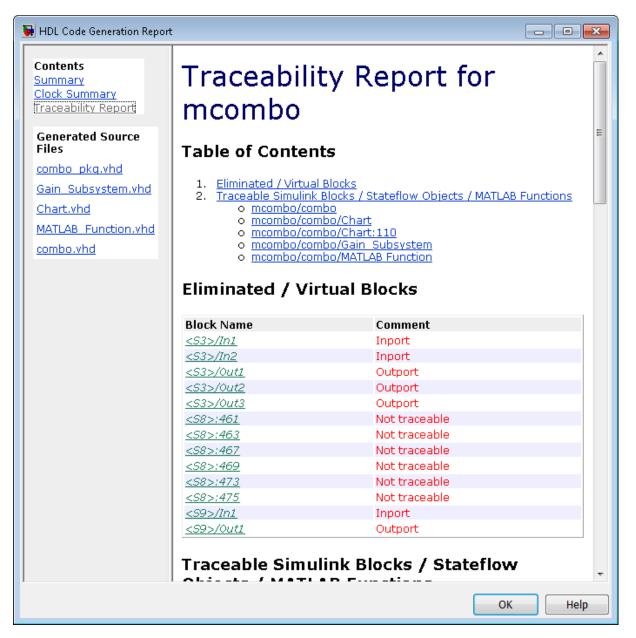

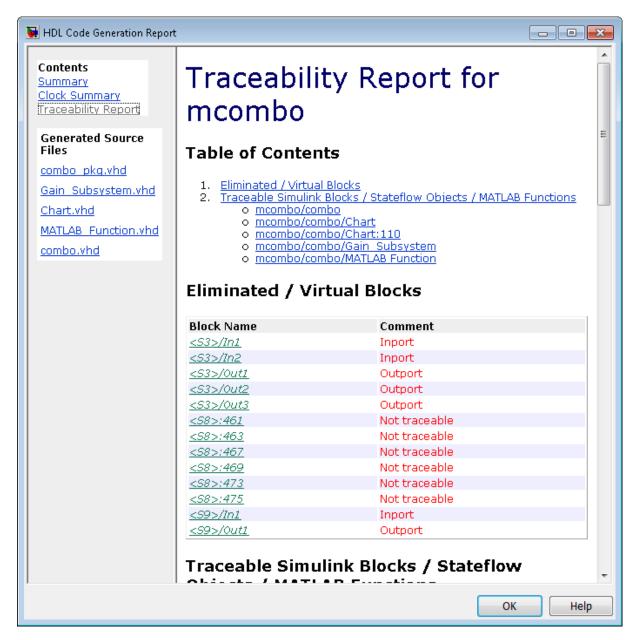

| Summary Section10-3Traceability Report Section10-5Generating a Traceability Report from ConfigurationParameters10-8Generating a Traceability Report from the CommandLine10-13Keeping the Report Current10-16Tracing from Code to Model10-16Tracing from Model to Code10-18Mapping Model Elements to Code Using the TraceabilityReport10-21Traceability Report Limitations10-23Resource Utilization Report Section10-23 | Creating and Using Code Generation Reports          | 10-2  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------|

| Traceability Report Section10-5Generating a Traceability Report from Configuration10-8Parameters10-8Generating a Traceability Report from the Command10-13Line10-13Keeping the Report Current10-16Tracing from Code to Model10-16Tracing from Model to Code10-18Mapping Model Elements to Code Using the Traceability10-21Traceability Report10-23Resource Utilization Report Section10-23                             | Information Included in Code Generation Reports     | 10-2  |

| Generating a Traceability Report from Configuration<br>Parameters10-8Generating a Traceability Report from the Command<br>Line10-13Keeping the Report Current10-16Tracing from Code to Model10-16Tracing from Model to Code10-18Mapping Model Elements to Code Using the Traceability<br>Report10-21Traceability Report Limitations10-23Resource Utilization Report Section10-23                                       | Summary Section                                     | 10-3  |

| Parameters10-8Generating a Traceability Report from the Command10-13Line10-13Keeping the Report Current10-16Tracing from Code to Model10-16Tracing from Model to Code10-18Mapping Model Elements to Code Using the Traceability10-21Traceability Report10-23Resource Utilization Report Section10-23                                                                                                                   | Traceability Report Section                         | 10-5  |

| Generating a Traceability Report from the Command<br>Line10-13Keeping the Report Current10-16Tracing from Code to Model10-16Tracing from Model to Code10-18Mapping Model Elements to Code Using the Traceability<br>Report10-21Traceability Report Limitations10-23Resource Utilization Report Section10-23                                                                                                            | Generating a Traceability Report from Configuration |       |

| Generating a Traceability Report from the Command<br>Line10-13Keeping the Report Current10-16Tracing from Code to Model10-16Tracing from Model to Code10-18Mapping Model Elements to Code Using the Traceability<br>Report10-21Traceability Report Limitations10-23Resource Utilization Report Section10-23                                                                                                            | Parameters                                          | 10-8  |

| Keeping the Report Current10-16Tracing from Code to Model10-16Tracing from Model to Code10-18Mapping Model Elements to Code Using the Traceability<br>Report10-21Traceability Report10-23Resource Utilization Report Section10-23                                                                                                                                                                                      |                                                     |       |

| Tracing from Code to Model10-16Tracing from Model to Code10-18Mapping Model Elements to Code Using the Traceability10-21Traceability Report10-23Resource Utilization Report Section10-23                                                                                                                                                                                                                               | Line                                                | 10-13 |

| Tracing from Code to Model10-16Tracing from Model to Code10-18Mapping Model Elements to Code Using the Traceability10-21Traceability Report10-23Resource Utilization Report Section10-23                                                                                                                                                                                                                               | Keeping the Report Current                          | 10-16 |

| Tracing from Model to Code10-18Mapping Model Elements to Code Using the Traceability10-21Report10-21Traceability Report Limitations10-23Resource Utilization Report Section10-23                                                                                                                                                                                                                                       |                                                     | 10-16 |

| Mapping Model Elements to Code Using the Traceability       10-21         Report       10-23         Traceability Report Limitations       10-23         Resource Utilization Report Section       10-23                                                                                                                                                                                                               |                                                     | 10-18 |

| Traceability Report Limitations10-23Resource Utilization Report Section10-23                                                                                                                                                                                                                                                                                                                                           |                                                     |       |

| Resource Utilization Report Section 10-23                                                                                                                                                                                                                                                                                                                                                                              | Report                                              | 10-21 |

| Resource Utilization Report Section 10-23                                                                                                                                                                                                                                                                                                                                                                              | Traceability Report Limitations                     | 10-23 |

|                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     | 10-23 |

| · ·                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     | 10-25 |

|                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                   |       |

#### Annotating Generated Code with Comments and

| Requirements |  | 10-27 |

|--------------|--|-------|

|--------------|--|-------|

| Simulink Annotations                                | 10-27 |

|-----------------------------------------------------|-------|

| Text Comments                                       | 10-27 |

| Requirements Comments and Hyperlinks                | 10-28 |

|                                                     |       |

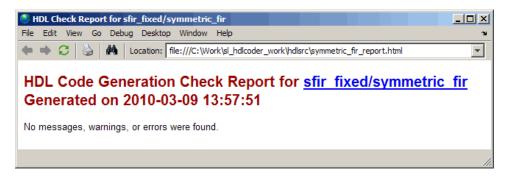

| HDL Compatibility Checker                           | 10 29 |

|                                                     | 10-02 |

|                                                     |       |

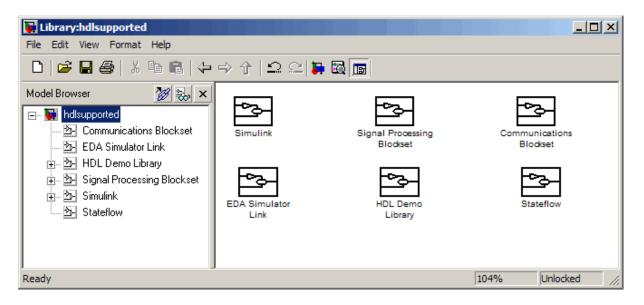

| Supported Blocks Library                            | 10-35 |

|                                                     |       |

| Code Tracing Using the Mapping File                 | 10-37 |

|                                                     | 10 01 |

|                                                     |       |

| Adding and Removing the HDL Configuration           |       |

| Component                                           | 10-40 |

| What Is the HDL Configuration Component?            | 10-40 |

| Adding the HDL Coder Configuration Component To a   |       |

| Model                                               | 10-40 |

| Removing the HDL Coder Configuration Component From |       |

| a Model                                             | 10-41 |

| a mouse                                             | 10-41 |

### Interfacing Subsystems and Models to HDL Code

| Overview of HDL Interfaces                                                                           | 11-2  |

|------------------------------------------------------------------------------------------------------|-------|

| <b>Generating a Black Box Interface for a Subsystem</b><br>Generating Code for a Black Box Subsystem | 11-3  |

| Implementation                                                                                       | 11-6  |

| Generating Reusable Code for Atomic Subsystems                                                       | 11-8  |

| Generating Interfaces for Referenced Models                                                          | 11-13 |

| Code Generation for Enabled and Triggered                                                            |       |

| Subsystems                                                                                           |       |

| Code Generation for Enabled Subsystems                                                               |       |

| Code Generation for Triggered Subsystems                                                             | 11-15 |

| Best Practices for Using Enabled and Triggered<br>Subsystems                                                          | 11-17   |

|-----------------------------------------------------------------------------------------------------------------------|---------|

| Code Generation for HDL Cosimulation Blocks                                                                           | 11-18   |

| Generating a Simulink Model for Cosimulation with an                                                                  |         |

| HDL Simulator                                                                                                         | 11 - 20 |

| Overview                                                                                                              | 11-20   |

| Generating a Cosimulation Model from the GUI                                                                          | 11 - 21 |

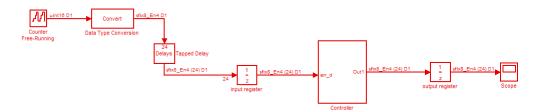

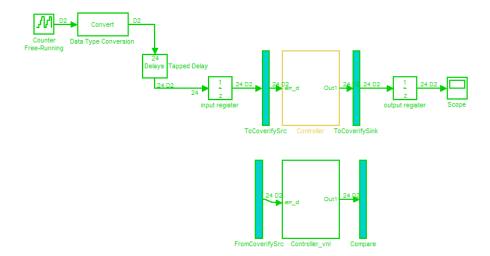

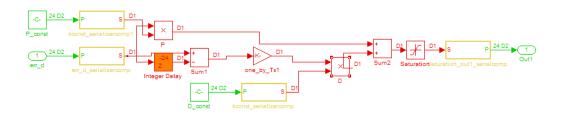

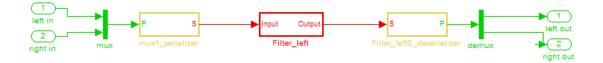

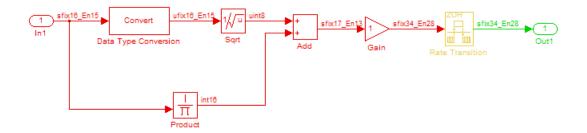

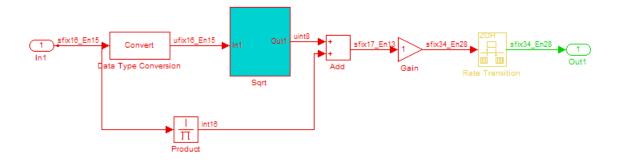

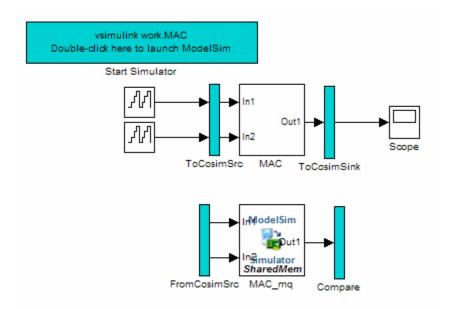

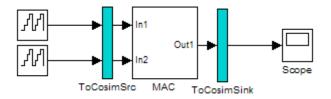

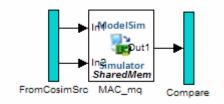

| Structure of the Generated Model                                                                                      | 11 - 27 |

| Launching a Cosimulation                                                                                              |         |

| The Cosimulation Script File                                                                                          |         |

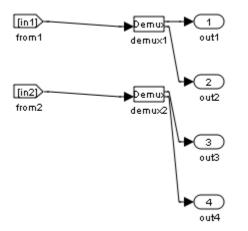

| Complex and Vector Signals in the Generated Cosimulation<br>Model<br>Generating a Cosimulation Model from the Command | 11-38   |

| Line                                                                                                                  | 11-40   |

| and Scripts                                                                                                           | 11-40   |

| Limitations for Cosimulation Model Generation                                                                         |         |

|                                                                                                                       |         |

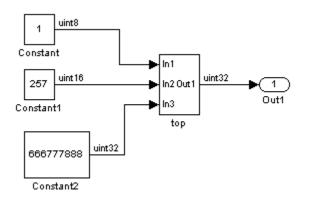

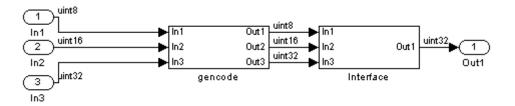

| Customizing the Generated Interface                                                                                   | 11-43   |

| Pass-Through and No-Op Implementations                                                                                | 11-47   |

| Limitation on Generated Verilog Interfaces                                                                            | 11-48   |

### **Stateflow HDL Code Generation Support**

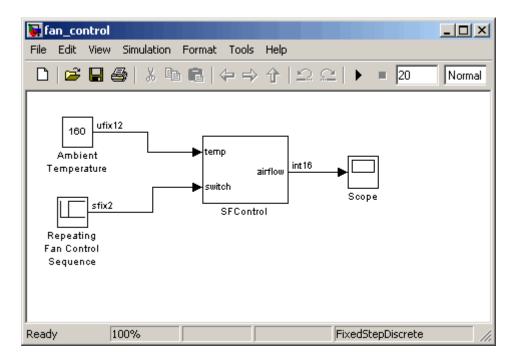

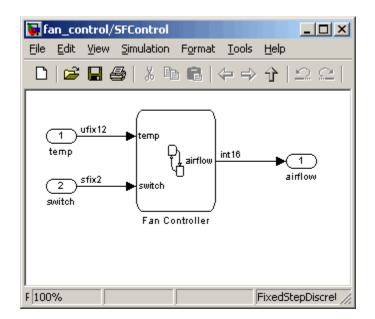

| Introduction to Stateflow HDL Code Generation      | 12-2   |

|----------------------------------------------------|--------|

| Overview                                           | 12-2   |

| Demos and Related Documentation                    | 12 - 2 |

|                                                    |        |

| Quick Guide to Requirements for Stateflow HDL Code |        |

| Generation                      | 12-4 |

|---------------------------------|------|

| Overview                        | 12-4 |

| Location of Charts in the Model | 12-4 |

| Data Type Usage                 | 12-4 |

| Chart Initialization                                         | 12-5    |

|--------------------------------------------------------------|---------|

| Registered Output                                            | 12-5    |

| Restrictions on Imported Code                                | 12-6    |

| Using Input and Output Events                                | 12-6    |

| Using For Loops                                              | 12-7    |

| Other Restrictions                                           | 12-7    |

|                                                              |         |

| Mapping Chart Semantics to HDL                               | 12-9    |

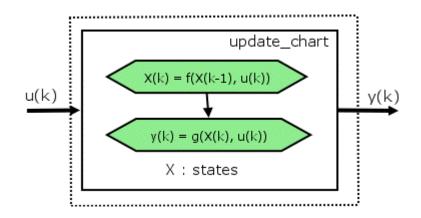

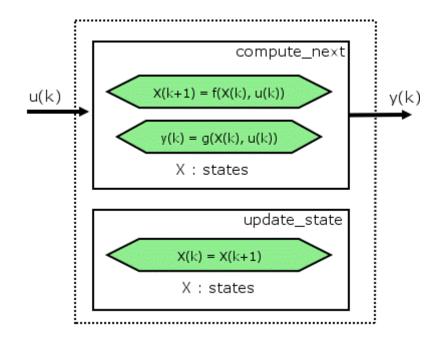

| Software Realization of Chart Semantics                      | 12-9    |

| Hardware Realization of Stateflow Semantics                  | 12-11   |

| Restrictions for HDL Realization                             | 12-14   |

| Using Mealy and Moore Machine Types in HDL Code              |         |

| Generation                                                   | 12-16   |

| Overview                                                     | 12-16   |

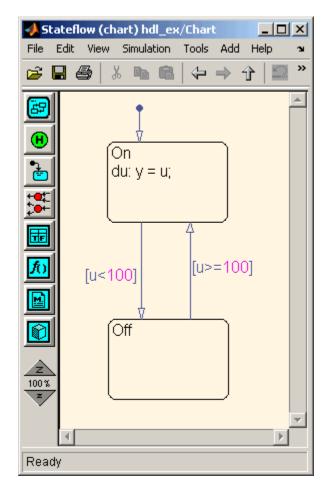

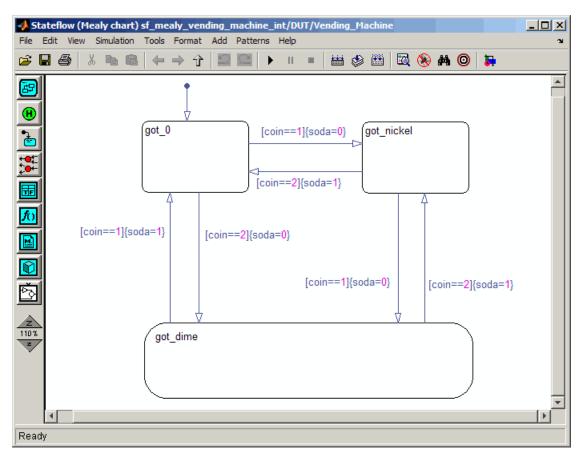

| Generating HDL for a Mealy Finite State Machine              | 12-17   |

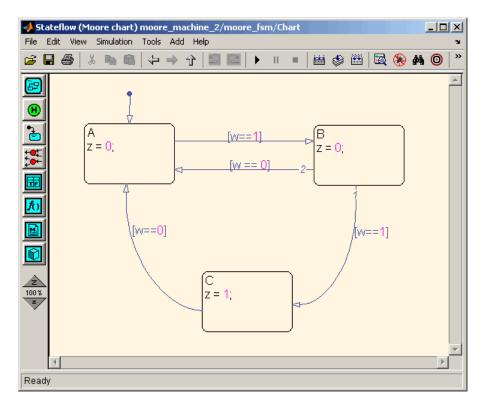

| Generating HDL Code for a Moore Finite State Machine $\dots$ | 12-21   |

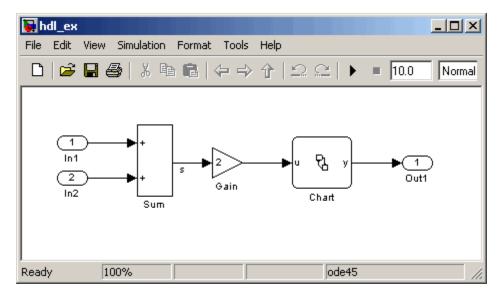

| Structuring a Model for HDL Code Generation                  | 12-26   |

|                                                              | 12 20   |

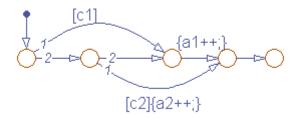

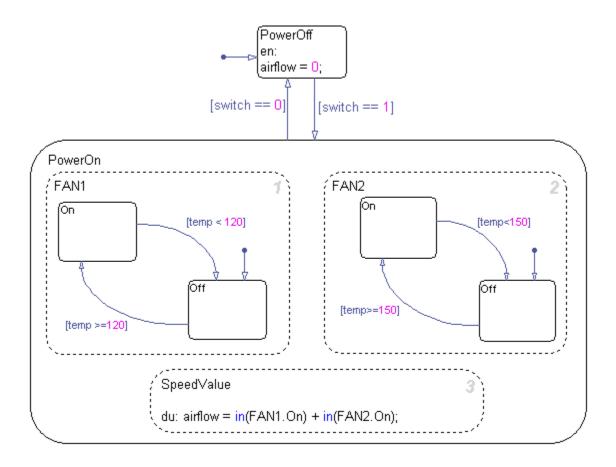

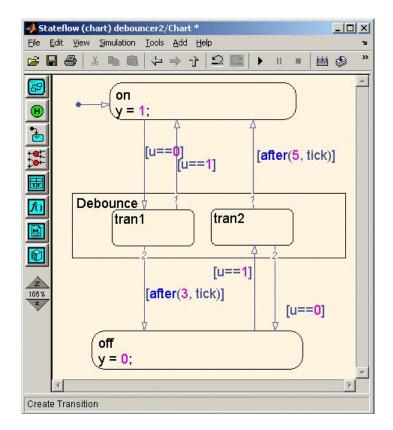

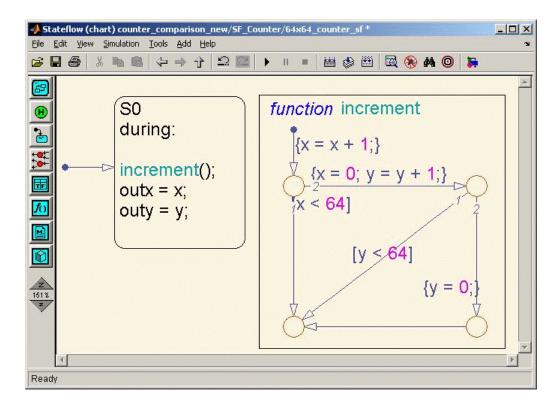

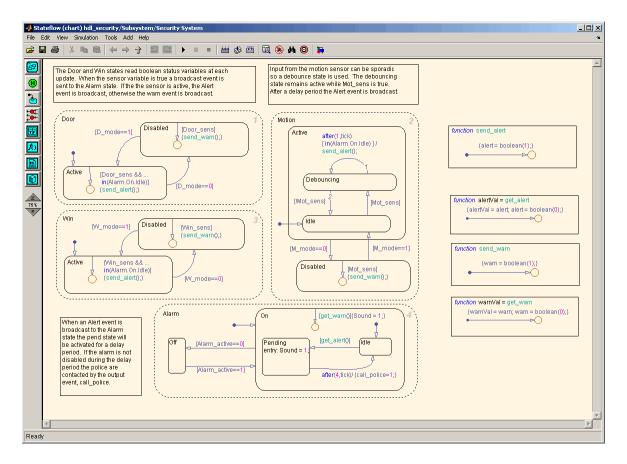

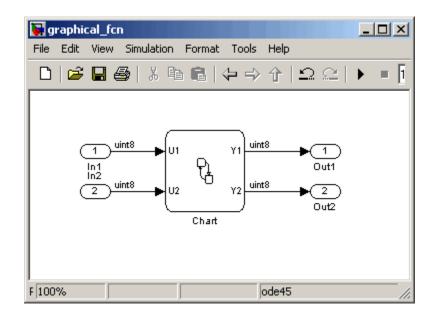

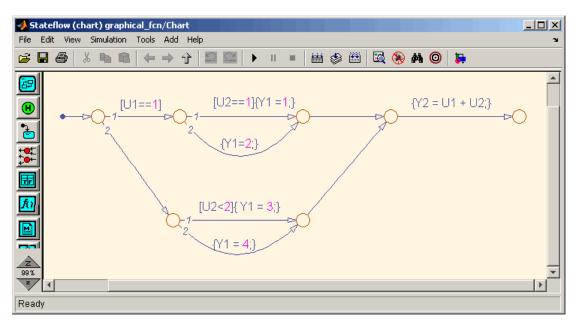

| Design Patterns Using Advanced Chart Features                | 12-32   |

| Temporal Logic                                               | 12 - 32 |

| Graphical Function                                           | 12 - 35 |

| Hierarchy and Parallelism                                    | 12 - 37 |

| Stateless Charts                                             | 12-41   |

| Truth Tables                                                 | 12-44   |

|                                                              |         |

### Generating HDL Code with the MATLAB Function Block

| Introduction                                   | 13-2   |

|------------------------------------------------|--------|

| HDL Applications for the MATLAB Function Block | 13 - 2 |

| Related Documentation and Demos                | 13-3   |

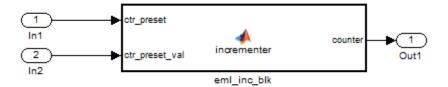

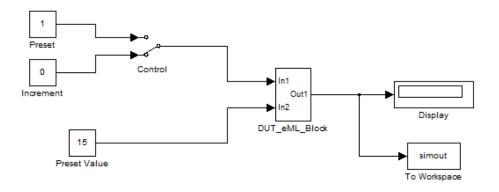

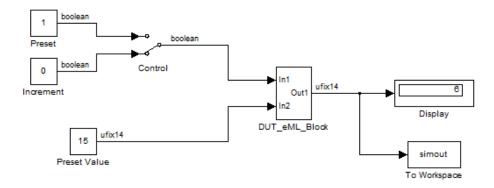

| Tutorial Example: Incrementer                  | 13-4   |

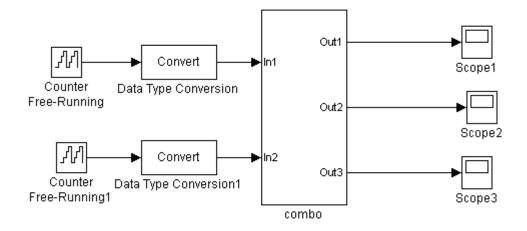

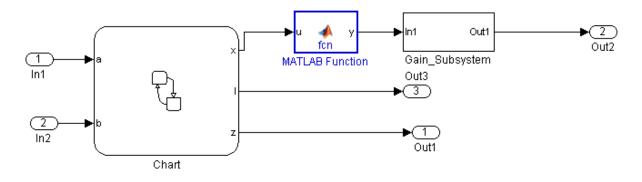

| Example Model Overview                         | 13-4   |

| Setting Up                                     | 13-7   |

| Creating the Model and Configuring General Model<br>Settings                                      | 13-7             |

|---------------------------------------------------------------------------------------------------|------------------|

| Adding a MATLAB Function Block to the Model<br>Setting Optimal Fixed-Point Options for the MATLAB | 13-8             |

| Function Block                                                                                    | 13-9             |

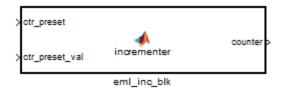

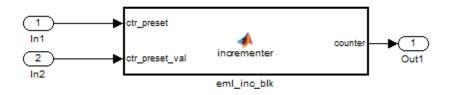

| Programming the MATLAB Function Block<br>Constructing and Connecting the DUT_eML_Block            | 13-12            |

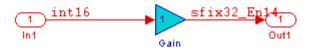

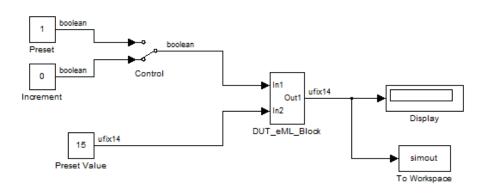

| Subsystem<br>Compiling the Model and Displaying Port Data Types                                   | 13-13<br>13-16   |

| Simulating the eml_hdl_incrementer_tut Model                                                      | 13-16            |

| Generating HDL Code                                                                               | 13-17            |

| Useful MATLAB Function Block Design Patterns for                                                  |                  |

| HDL                                                                                               | 13-20            |

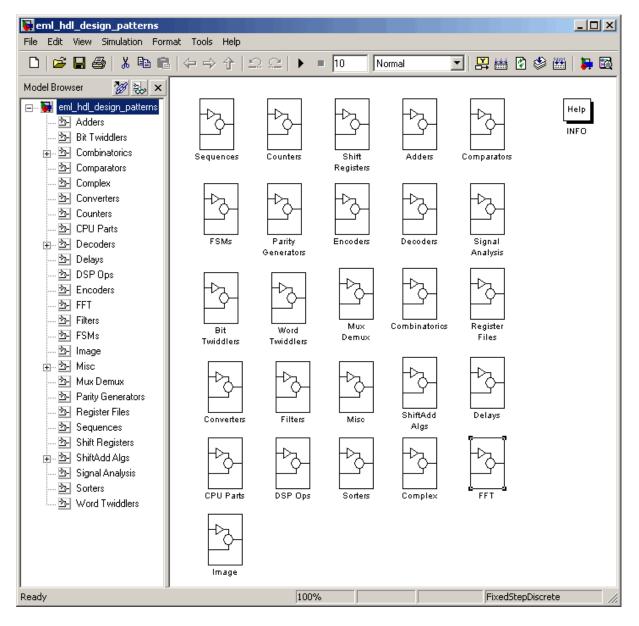

| The eml_hdl_design_patterns Library                                                               | 13-20            |

| Efficient Fixed-Point Algorithms<br>Using Persistent Variables to Model State                     | 13-22<br>13-26   |

| Creating Intellectual Property with the MATLAB Function<br>Block                                  | 13-27            |

| Modeling Control Logic and Simple Finite State                                                    | 10-27            |

| Machines                                                                                          | 13-28            |

| Modeling Counters                                                                                 | 13-30            |

| Modeling Hardware Elements                                                                        | 13-31            |

| Using Fixed-Point Bitwise Functions                                                               | 13-33            |

| Overview                                                                                          | 13-33            |

| Bitwise Functions Supported for HDL Code Generation                                               | 13-33            |

| Bit Slice and Bit Concatenation Functions<br>Shift and Rotate Functions                           | 13-39<br>13-40   |

|                                                                                                   | 10-40            |

| Using Complex Signals                                                                             | 13-44            |

| Introduction                                                                                      | 13-44            |

| Declaring Complex Signals                                                                         | 13-44            |

| Conversion Between Complex and Real Signals                                                       | 13-46            |

| Arithmetic Operations on Complex Numbers                                                          | 13-46            |

| Support for Vectors of Complex Numbers<br>Other Operations on Complex Numbers                     | $13-50 \\ 13-51$ |

| Other Operations on Complex Numbers                                                               | 10-01            |

| Distributed Pipeline Insertion for MATLAB Function                                                | 10 50            |

| Blocks                                                                                            | $13-53 \\ 13-53$ |

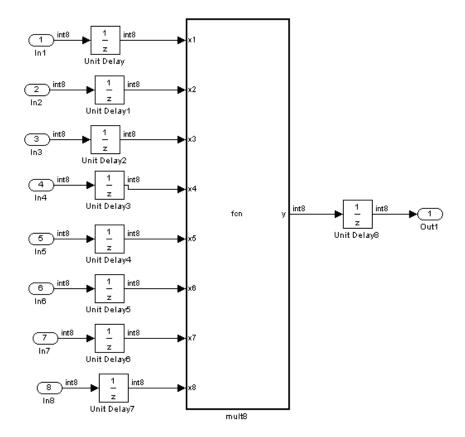

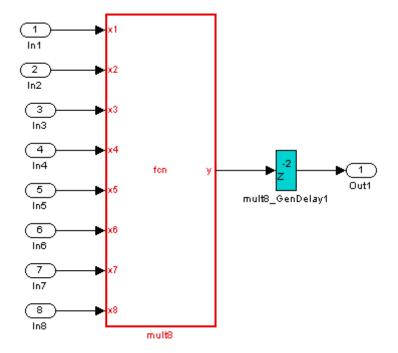

| Overview<br>Example: Multiplier Chain                                                             | 13-53            |

|                                                                                                   | <b>TO 00</b>     |

| Recommended Practices                                                              | 13-60                   |

|------------------------------------------------------------------------------------|-------------------------|

| Introduction                                                                       | 13-60                   |

| Use Compiled External Functions With MATLAB Function                               |                         |

| Blocks                                                                             | 13-60                   |

| Build the MATLAB Function Block Code First                                         | 13-60                   |

| Use the hdlfimath Utility for Optimized FIMATH                                     |                         |

| Settings                                                                           | 13-61                   |

| Use Optimal Fixed-Point Option Settings                                            | 13-63                   |

| Language Support<br>Fixed-Point Runtime Library Support<br>Variables and Constants | 13-65<br>13-65<br>13-66 |

| Use of Nontunable Parameter Arguments                                              | 13-69                   |

| Arithmetic Operators                                                               | 13-70                   |

| Relational Operators                                                               | 13-71                   |

| Logical Operators                                                                  | 13-71                   |

| Control Flow Statements                                                            | 13-72                   |

| Other Limitations                                                                  | 13-74                   |

### Generating Scripts for HDL Simulators and Synthesis Tools

| Overview of Script Generation for EDA Tools                                                                                                | 14-2                         |

|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Defaults for Script Generation                                                                                                             | 14-3                         |

| Custom Script Generation         Overview         Structure of Generated Script Files         Properties for Controlling Script Generation | 14-4<br>14-4<br>14-4<br>14-5 |

| Controlling Script Generation with the EDA Tool Scripts<br>GUI Pane                                                                        | <b>14-9</b>                  |

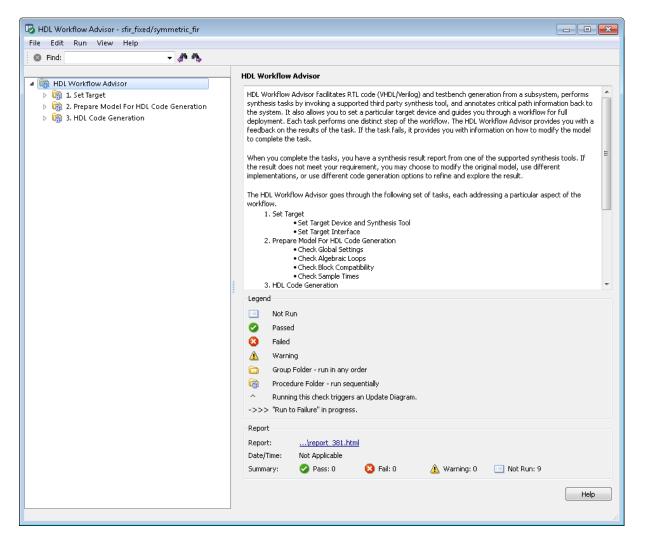

| What Is the HDL Workflow Advisor?                                           | 15-2                                                       |

|-----------------------------------------------------------------------------|------------------------------------------------------------|

| HDL Workflow Advisor Compatibility with Third-Party<br>Tools                | 15-3                                                       |

| Supported Third-Party Synthesis Tools<br>Setting Up the Synthesis Tool Path | $15-3 \\ 15-3$                                             |

| Starting the HDL Workflow Advisor                                           | 15-5                                                       |

| Using the HDL Workflow Advisor Window                                       | 15-7                                                       |

| Selecting and Running HDL Workflow Advisor                                  |                                                            |

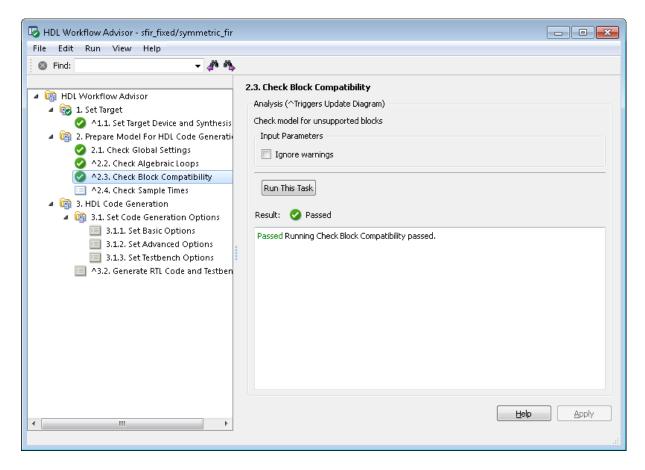

| Tasks                                                                       | 15-10                                                      |

| Task Execution Order                                                        | 15-10                                                      |

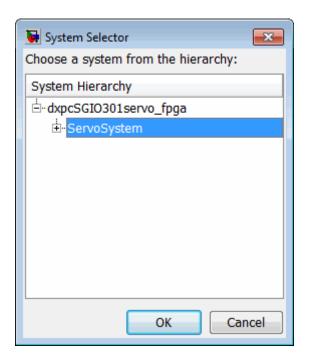

| Changing the Device Under Test                                              | 15-12                                                      |

| Selecting and Running Tasks Individually                                    | 15-13                                                      |

| Selecting and Running a Sequence of Tasks                                   | 15-16                                                      |

| Saving and Restoring the HDL Workflow Advisor                               |                                                            |

| State                                                                       | 15 - 22                                                    |

| How the Save and Restore Process Works                                      | 15 - 22                                                    |

| Limitations of the Save and Restore Process                                 | 15 - 22                                                    |

| Saving the HDL Workflow Advisor State                                       | 15 - 22                                                    |

| Restoring the HDL Workflow Advisor State                                    | 15 - 25                                                    |

|                                                                             |                                                            |

| Correcting a Warning or Failure Problem                                     | 15-26                                                      |

|                                                                             |                                                            |

| Generating HDL Workflow Advisor Reports                                     | 15-29                                                      |

| Viewing HDL Workflow Advisor Reports                                        | 15-29                                                      |

| Saving HDL Workflow Advisor Reports                                         | 15-33                                                      |

|                                                                             |                                                            |

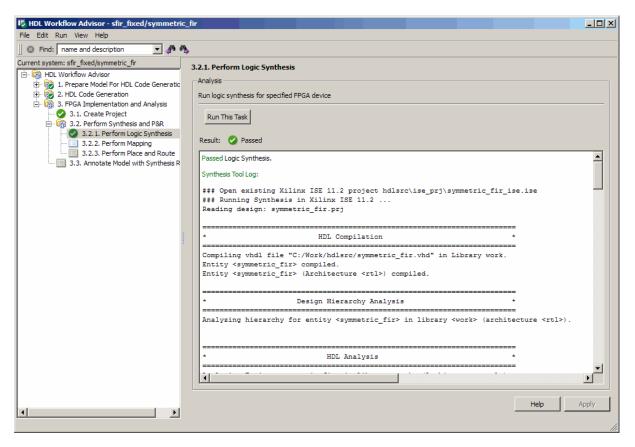

| Performing FPGA Synthesis and Analysis Tasks with                           | 15 94                                                      |

| Third-Party Tools                                                           | 15-34                                                      |

| FPGA Synthesis and Analysis Tasks Overview                                  | $\begin{array}{c} 15\text{-}34\\ 15\text{-}34 \end{array}$ |

| Creating a Synthesis Project                                                | 15-34<br>15-37                                             |

| Performing Logic Synthesis                                                  | 19-97                                                      |

| Performing Mapping                                                                                            |         |

|---------------------------------------------------------------------------------------------------------------|---------|

| Performing Place and Route                                                                                    | 19-39   |

| Annotating Your Model with Critical Path                                                                      |         |

| Information                                                                                                   | 15-42   |

|                                                                                                               |         |

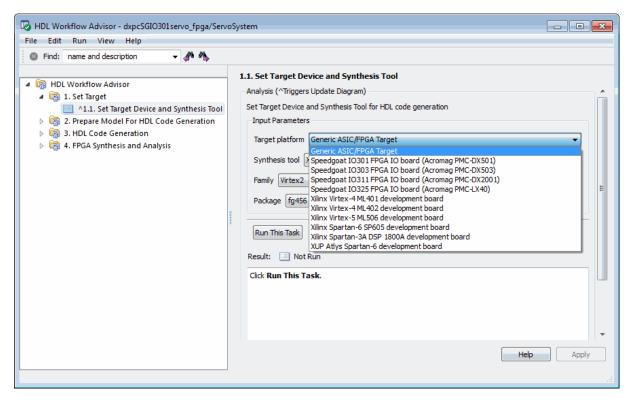

| Automated Workflows for Specific Target Devices and<br>Synthesis Tools                                        | 15-46   |

|                                                                                                               | 10-40   |

| Workflow for Speedgoat FPGA IO Boards and xPC                                                                 |         |

| Target                                                                                                        | 15-48   |

| Selecting a Speedgoat Target Device                                                                           | 15 - 48 |

| Setting the Target Interface for Speedgoat Boards<br>Code Generation, Synthesis, and Generation of xPC Target |         |

| Interface Subsystem                                                                                           | 15-58   |

|                                                                                                               |         |

| Workflow for Xilinx FPGA Development Boards                                                                   | 15-63   |

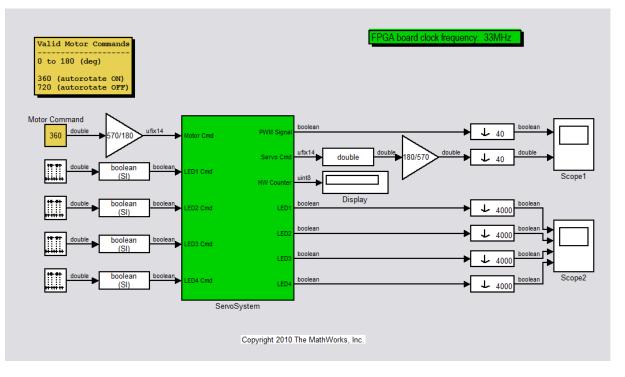

| Example Model                                                                                                 | 15-63   |

| Selecting the Target Device                                                                                   | 15-64   |

| Setting the Target Interface                                                                                  | 15-68   |

| Code Generation, Synthesis, and Programming of Target                                                         |         |

| Device                                                                                                        | 15-72   |

### HDL Workflow Advisor Tasks

| HDL Workflow Advisor Tasks                     | 16-2  |

|------------------------------------------------|-------|

| HDL Workflow Advisor Tasks Overview            | 16-3  |

| Set Target Overview                            | 16-5  |

| Set Target Device and Synthesis Tool           | 16-6  |

| Set Target Interface                           | 16-7  |

| Prepare Model For HDL Code Generation Overview | 16-8  |

| Check Global Settings                          | 16-9  |

| Check Algebraic Loops                          | 16-10 |

| Check Block Compatibility                      | 16-11 |

| Check Sample Times                             | 16-12 |

| HDL Code Generation Overview                   | 16-13 |

| Set Code Generation Options Overview           | 16-14 |

| Set Basic Options                              | 16-15 |

|                                                |       |

| Set Advanced Options                        | 16-16        |

|---------------------------------------------|--------------|

| Set Testbench Options                       | 16-17        |

| Generate RTL Code and Testbench             | 16-18        |

| FPGA Synthesis and Analysis Overview        | 16-19        |

| Create Project                              | 16-20        |

| Perform Synthesis and P/R Overview          | 16-21        |

| Perform Logic Synthesis                     | 16-22        |

| Perform Mapping                             | 16-23        |

| Perform Place and Route                     | <b>16-24</b> |

| Annotate Model with Synthesis Result        | 16-25        |

| Download to Target Overview                 | 16-26        |

| Generate Programming File                   | 16-27        |

| Program Target Device                       | 16-28        |

| Generate xPC Target Interface               | 16-29        |

| Save and Restore HDL Workflow Advisor State | 16-30        |

### **Code Generation Control Files**

| <b>READ THIS FIRST: Control File Compatibility and</b> |       |

|--------------------------------------------------------|-------|

| Conversion Issues                                      | 17-2  |

| Conversion From Use of Control Files Recommended       | 17-2  |

| Detaching Existing Models From Control Files           | 17-2  |

| Applying Control File Settings                         | 17-3  |

| Backwards Compatibility                                | 17-3  |

| Overview of Control Files                              | 17-4  |

| What Is a Control File?                                | 17-4  |

| Selectable Block Implementations and Implementation    |       |

| Parameters                                             | 17-5  |

| Implementation Mappings                                | 17-6  |

| Structure of a Control File                            | 17-7  |

| Code Generation Control Objects and Methods            | 17-9  |

| Overview                                               | 17-9  |

| hdlnewcontrol                                          | 17-9  |

| forEach                                                | 17-9  |

| forAll                                                 | 17-14 |

| set                                                | 17 - 14        |

|----------------------------------------------------|----------------|

| generateHDLFor                                     | 17 - 15        |

| hdlnewcontrolfile                                  |                |

| Using Control Files in the Code Generation Process | 17-17          |

| Where to Locate Your Control Files                 |                |

| Making Your Control Files More Portable            |                |

|                                                    |                |

| Specifying Block Implementations and Parameters in | 1 . 10         |

| the Control File                                   |                |

|                                                    |                |

| the Control File                                   | 17-18          |

| the Control File                                   | 17-18<br>17-19 |

### ${\bf Properties-Alpha betical\ List}$

## 18

### **Property Reference**

| Language Selection Properties                | 19-2 |

|----------------------------------------------|------|

| File Naming and Location Properties          | 19-2 |

| Reset Properties                             | 19-2 |

| Header Comment and General Naming Properties | 19-3 |

| Script Generation Properties                 | 19-4 |

| Port Properties            | 19-5  |

|----------------------------|-------|

| Advanced Coding Properties | 19-6  |

| Test Bench Properties      | 19-8  |

| Generated Model Properties | 19-10 |

### ${\bf Functions-Alpha betical\ List}$

## 20

### **Function Reference**

| 7 | 1 |

|---|---|

|   |   |

| Code Generation Functions               | 21-2 |

|-----------------------------------------|------|

| HDL Block and Model Parameter Utilities | 21-3 |

| Utility Functions                       | 21-4 |

| Control File Utilities                  | 21-5 |

### Examples

### A

| Generating HDL Code Using the Command Line |     |

|--------------------------------------------|-----|

| Interface                                  | A-2 |

| Generating HDL Code Using the GUI          | A-2 |

Index

# Getting Started

- "Product Overview" on page 1-2

- "Expected Users and Prerequisites" on page 1-5

- "Software Requirements and Installation" on page 1-6

- "Available Help and Demos" on page 1-8

### **Product Overview**

#### In this section ...

"Automated HDL Code Generation in the Hardware Development Process" on page 1-2

"Summary of Key Features" on page 1-4

### Automated HDL Code Generation in the Hardware Development Process

Simulink<sup>®</sup> HDL Coder<sup>™</sup> software lets you generate hardware description language (HDL) code based on Simulink<sup>®</sup> models and Stateflow<sup>®</sup> finite-state machines. The coder brings the Model-Based Design approach into the domain of application-specific integrated circuit (ASIC) and field programmable gate array (FPGA) development. Using the coder, system architects and designers can spend more time on fine-tuning algorithms and models through rapid prototyping and experimentation and less time on HDL coding.

Typically, you use a Simulink model to simulate a design intended for realization as an ASIC or FPGA. Once satisfied that the model meets design requirements, you run the Simulink HDL Coder compatibility checker utility to examine model semantics and blocks for HDL code generation compatibility. You then invoke the coder, using either the command line or the graphical user interface. The coder generates VHDL or Verilog code that implements the design embodied in the model.

Usually, you also generate a corresponding test bench. You can use the test bench with HDL simulation tools to drive the generated HDL code and evaluate its behavior. The coder generates scripts that automate the process of compiling and simulating your code in these tools. You can also use EDA Simulator Link<sup>TM</sup>, software from MathWorks<sup>®</sup> to cosimulate generated HDL entities within a Simulink model.

The test bench feature increases confidence in the correctness of the generated code and saves time spent on test bench implementation. The design and test process is fully iterative. At any point, you can return to the original model, make modifications, and regenerate code.

When the design and test phase of the project has been completed, you can easily export the generated HDL code to synthesis and layout tools for hardware realization. The coder generates synthesis scripts for the Synplify<sup>®</sup> family of synthesis tools.

#### **Extending the Code Generation Process**

There are a number of ways to extend the code generation process.

You can direct many details of the code generation process by setting code generation options in the **HDL Code Generation** pane of the Configuration Parameters dialog box or the Model Explorer. You can also set code generation options as parameter/value pairs passed to the makehdl and makehdltb functions.

You can also specify how code is generated for a selected block or sets of blocks within the model. The coder provides alternate HDL *block implementations* for a variety of blocks. The **HDL Block Properties** dialog box lets you select from among implementations optimized for characteristics such as speed, chip area, or low latency. The **HDL Block Properties** dialog box also lets you set *implementation parameters* that specify further details of the code generated for a block.

You can also select implementations and apply implementation parameters to large groups of blocks programmatically. The coder provides utility functions such as hdlfind\_system and hdlset\_param for this purpose.

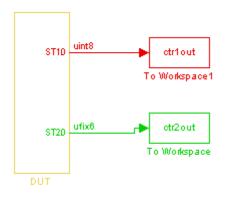

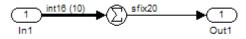

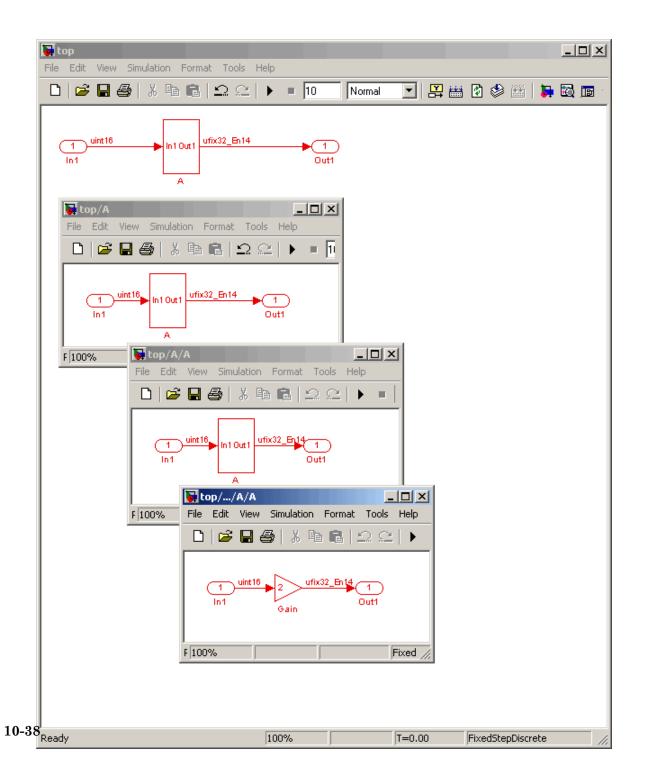

In some cases, block-specific optimizations may introduce latencies (delays) or numeric computations (for example, saturation or rounding operations) in the generated code that are not in the original model. To help you evaluate such cases, the coder creates a *generated model* — a Simulink model that corresponds exactly to the generated HDL code. This generated model lets you run simulations that produce results that are bit-true to the HDL code, and whose timing is cycle-accurate with respect to the HDL code.

You can interface generated HDL code to existing or legacy HDL code. One way to do this is to use a subsystem in your model as a placeholder for an HDL entity, and generate a*black box* interface (comprising I/O port definitions only) to that entity. Another way is to generate a cosimulation interface by placing an HDL Cosimulation block in your model.

1

### **Summary of Key Features**

- Generation of target-independent, synthesizable HDL code from Simulink models, MATLAB code, and Stateflow charts

- Support for Mealy and Moore finite-state machines and control logic implementations

- Generation of test benches and EDA Simulator Link cosimulation models

- Resource sharing and subsystem-level retiming options for area-speed tradeoffs

- Simulink model optimization using timing constraint information and HDL synthesis tools

- Code-to-model and model-to-code traceability for DO-254

- Legacy code integration

### **Expected Users and Prerequisites**

Users of this product are system and hardware architects and designers who develop, optimize, and verify ASICs or FPGAs. These designers are experienced with VHDL or Verilog but can benefit from automated HDL code generation.

Users are expected to have prerequisite knowledge in the following areas:

- Hardware design and system integration

- VHDL or Verilog

- MATLAB®

- Simulink

- Simulink<sup>®</sup> Fixed Point<sup>™</sup>

- DSP System Toolbox<sup>™</sup>

- HDL simulators, such as the Mentor Graphics<sup>®</sup> ModelSim<sup>®</sup> simulator or Cadence Incisive<sup>®</sup> simulator

- Synthesis tools, such as Synplify

### Software Requirements and Installation

#### In this section...

"Software Requirements" on page 1-6

```

"Installing the Software" on page 1-7

```

#### **Software Requirements**

The coder requires the following MathWorks software:

- MATLAB

- Simulink